タイミングデバイスの「限界突破」、MEMS振動子内蔵のクロックジェネレーター

SiTimeがAIデータセンター向けにクロックジェネレーターIC「Chorus」ファミリーを発表。

Chorusは小型で耐久性が高く、最大4個の水晶発振器を置き換えて基板面積を最大50%削減可能。

データセンターでは多くのタイミングデバイスが必要であり、Chorusはそうしたニーズに応える。

設計時間を最大6週間短縮できる利点もある。

Chorusには高い位相ジッタが異なる2種類があり、データセンターや自動車向けなど幅広い用途で期待されている。

SiTimeは一部の顧客にサンプルを提供中で、2024年下期に正式出荷予定。

米SiTimeは2024年5月13日、AI(人工知能)データセンター向けに、クロックジェネレーターIC「Chorus(コーラス)」ファミリーを発表した。シリコンMEMS振動子、発振回路、クロックを統合した製品となる。既存のクロックジェネレーターICに比べ、半分のサイズで約10倍の耐久性を実現している他、最大4個の水晶発振器を1個のChorusで置き換えられるので、タイミング回路の基板面積を最大50%削減できるという。

Chorusがターゲットとするデータセンターでは、ラック内外で数多くのタイミングデバイスが使われている。ラック内では、NIC(Network Interface Card)/スマートNICに1~3個、アクセラレーターカードに4~8個、ラック外ではプラガブル光モジュールに1~2個、コアスイッチに8~24個といった具合だ。さらに、生成AIの普及で、データセンターの低消費電力化や性能向上が求められる中、高精度なタイミングデバイスの重要性が増している。

SiTimeのマーケティング担当上級副社長を務めるPiyush Sevalia氏は、Chorusはこうしたニーズに応える製品だと強調する。特に、タイミングソリューション(システムクロックツリー)に必要な実装面積の削減や信頼性の向上を実現すると述べる。

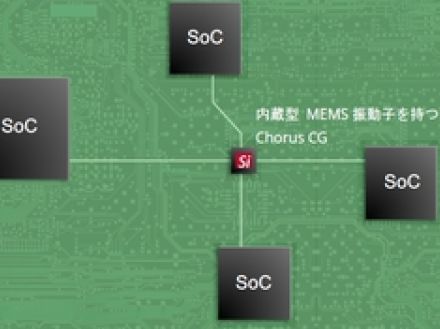

一例として、データセンター向けの通信用ボードに複数のSoC(System on Chip)が搭載されている場合、それぞれのSoCの駆動には1個ずつ外付けの水晶発振器が必要になる。一方、Chorusは最大4個のSoCを1個のChorusで駆動できるため、タイミングソリューション全体の実装面積を最大で50%縮小できるとする。加えてChorusはクロック間で同期を取れることも特長だ。

設計時間の短縮にも効く。従来のクロックジェネレーターICは、駆動のために外付けの水晶振動子が必要になる。ただしこれは、クロックジェネレーターICと水晶振動子間におけるインピーダンス不一致や、配線上のノイズカップリングといった問題を招く。これを解決するために設計の調整が必要になり、その結果3~4週間の設計遅延が発生してしまうという。それに対し、MEMS振動子を内蔵したChorusは、そうした調整の必要がなくなるので、システムクロックアーキテクチャを簡素化するとともに、設計期間を最大6週間短縮するとしている。

Chorusには、位相ジッタが異なる2種類がある。150フェムト秒の「SiT91211」と70フェムト秒の「SiT91213」だ。いずれも出力周波数は1M~700MHzの範囲で設定でき、最大4つの差動出力または8つのLVCMOS出力が可能。パッケージは4×4mmの24端子QFNである。

データセンターやAI関連の製品がメインターゲットだが、信頼性や耐久性が高いことから自動車や産業機器、航空宇宙/防衛などの用途も見込む。自動車向けには、AEC-Q100などの認証を取得予定だという。Sevalia氏によれば、日本では自動車や産業機器などがターゲットになる。

SiTimeは一部の顧客に向けてChorusのサンプルを提供中で、通常のサンプル出荷は2024年下期に開始する予定だ。