Zen 5は前世代からIPCが16%向上。3nm版も登場か?AMDがCPUの詳細を明らかに

AMDはZen 5アーキテクチャを搭載した新しいCPU製品を発表し、各パーツに大幅な強化が施されている。

Zen 5ではフロントエンドや実行ユニット、バックエンドが改善され、性能向上に貢献している。

また、Zen 5はTSMCの4nmと3nmに最適化されており、IPCが16%向上している。

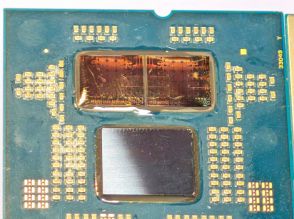

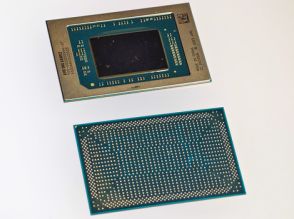

AMDは6月のCOMPUTEX TAIPEI 2024開催時に、ノートPC向けのRyzen AI 300シリーズ、デスクトップPC向けのRyzen 9000シリーズといった、新しいCPUアーキテクチャ「Zen 5」を搭載した製品を発表している。そのときは概要の紹介のみにとどまっていたが、7月15日(現地時間)についに詳細が明らかにされた。

■ 実行ユニットに大きく手が入ったZen 5

Zen 5のアーキテクチャは、フロントエンド(デコーダなど)、実行ユニット(スケジューラやALUなど)、バックエンド(ロード/ストア、データキャッシュなど)のいずれも手が入れられており、前世代となる「Zen 4」に比べて同クロックでも性能が向上していることが大きな特徴となる。

フロントエンドでは、デコーダとOp Cacheに大きく手が入っている。従来のZen 4のデコーダは1クロックサイクルあたり4命令を内部命令に変換できるようになっていたが、Zen 5では1クロックサイクルあたり4命令は変わっていないものの、そのデコーダユニットがデュアルパイプになっており、1クロックあたり4命令×2でデコード可能になっている。

また、そのデコードされた内部命令を保存しておくOp Cacheもデュアル化されており、Zen 4では1クロックサイクルで9内部命令となっていたが、Zen 5では1クロックサイクルで6内部命令×2(つまり12内部命令)が処理できる。

これらの強化により分岐予測の低遅延、正確性の向上、スループットの向上などが実現され、実行ユニットに命令を引き渡すディスパッチも1クロックサイクルでZen 4の6内部命令から8内部命令に引き上げられている。

要するに、x86命令をより内部命令に多く変換可能になっているということだ。

実行ユニットも同様で、整数演算器では内部の実行ユニットが2つ増やされている。Zen 4ではALUが5、AGUが3という8つの演算ユニットが用意されていたが、Zen 5ではALUが6、AGUが4となり、合計で10個の演算装置を利用して演算できる。

それに合わせてレジスタファイルも増やされており、Zen 4の224からZen 5では240に強化されているほか、スケジューラはZen 4に比べてより大型の統合されたスケジューラに強化されており、より効率よく整数演算を行なうことが可能になっている。

浮動小数点演算器も同様でスケジューラがZen 4世代の2つから3つに増やされているほか、Zen 4世代ではレジスタファイルが256bitになっていたため、AVX512の実行には2クロックサイクルが必要になっていたが、Zen 5ではレジスタファイルが512bitに強化され、1クロックサイクルでAVX512命令を行なえるようになっている。

また、浮動小数点演算ユニットのうちFADDの低遅延化が実現されるなどの強化で、より多くの浮動小数点命令を同時に処理可能になった。

バックエンドでの強化では、L1データキャッシュが32KB(8ウェイ、3ロード/2ストア)から48KB(12ウェイ、4ロード/2ストア)へと強化されている。これにより、L1キャッシュの帯域幅は2倍になり、データの読み込み速度が大きく向上している。

■ TSMCの4nm、3nmに最適化

AMDによれば、Zen 4世代の強化では主にフロントエンドとバックエンド(ロードストア)の強化が大きかったが、Zen 5では実行ユニットの強化が性能向上に大きく貢献しているとのことで、整数演算器と浮動小数点演算器それぞれが強化され、性能向上につながっていることが分かる。

Zen 5の性能向上は、同じクロック周波数で比較した場合、平均して16%の性能向上が確認できるという。つまり、IPCが16%向上しているわけだ。

Zen 5はTSMCの4nmと3nmに最適化されているという。今回同時に発表されたノートPC向けのRyzen AI 300シリーズ、デスクトップPC向けのRyzen 9000シリーズはいずれも4nmで製造されており、今後どこかのタイミングで登場する将来の製品では3nmで製造されるオプションがあるということだ。

また、Zen 5にはL3キャッシュをCPUコア1つあたり1MBにした「Zen 5c」のオプションが用意されており、小型CPUデザインとして活用することもできる。

このZen 5cは、異種混合(ヘテロジニアス)なCPUコアとして、Intel的な言い方をするならEコアとしてRyzen AI 300シリーズに採用されているほか、将来的には第4世代EPYCでそうであったように、高密度バージョンとして第5世代EPYCで採用される可能性がある。

なお、AMDはこのZen 5の後継としてZen 6、そのコンパクトバージョンとしてZen 6cを開発していることをすでに明らかにしている。