半導体基板に3㎛の穴、東大などがレーザー加工技術を開発した意義

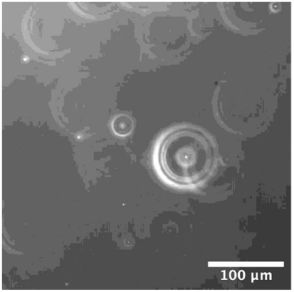

東京大学と味の素ファインテクノ(川崎市川崎区)、三菱電機、スペクトロニクス(大阪府吹田市)は、次世代の半導体製造後工程に使用されるパッケージ基板向けに、3マイクロメートルの微細な穴を開けるレーザー加工技術を開発した

共同チームは、深紫外(DUV)レーザー加工機を使い、層間絶縁膜への微細な穴開け加工を実現し、自由な穴開けパターンを基板上に高速に作製可能とした。

この技術は、将来のハイパフォーマンスコンピューターの発展などに役立ち、チップレット技術の高機能化を促すことが期待されている。

東京大学と味の素ファインテクノ(川崎市川崎区)、三菱電機、スペクトロニクス(大阪府吹田市)は共同で、次世代の半導体製造後工程に使うパッケージ基板に、既存技術より1ケタ小さい直径3マイクロメートル(マイクロは100万分の1)の微細な穴を開けられるレーザー加工技術を開発した。基板間を高密度に配線でき、生成人工知能(AI)などに必要なハイパフォーマンスコンピューターの発展などに役立つ。

共同チームは、次世代半導体の基板加工技術である深紫外(DUV)レーザー加工機を使い、層間絶縁膜への微細な穴開け加工を実現した。自由な穴開けパターンを基板上に高速に作製可能。構成要素ごとに別チップを作り、パッケージ基板上に一体化して実装する「チップレット」技術の高機能化を促す。

現在、チップ実装基板の層間配線として使っているのは、直径40マイクロメートルの穴。チップの微細化に伴い、将来はパッケージ基板の穴径は5マイクロメートル以下が求められているが、現行のレーザー加工技術は光学系などの特性により小さい径に集光することなどが困難だった。

米国で開かれた半導体パッケージ分野で世界最大の国際会議(ECTC)で発表した。東大など、レーザー加工技術を開発 半導体基板に3マイクロメートルの穴